随着集成电路尺寸的持续微缩,特别是进入亚3nm工艺节点,单纯通过缩小晶体管尺寸带来的性能提升已经逐渐变得困难。传统的二维(2D)芯片面临着“互连延迟”和“面积瓶颈”等挑战,导致继续依赖缩小尺寸来提升性能的道路越来越狭窄。此时,三维集成电路(3D IC)技术的出现,为摩尔定律的延续提供了新的解决思路。相比于传统通过硅通孔(TSV)实现的芯片堆叠封装,单片集成三维集成电路(Monolithic 3D IC, M3D)凭借其纳米级的垂直互连密度,成为了实现后摩尔时代高算力、低功耗系统的关键技术之一。

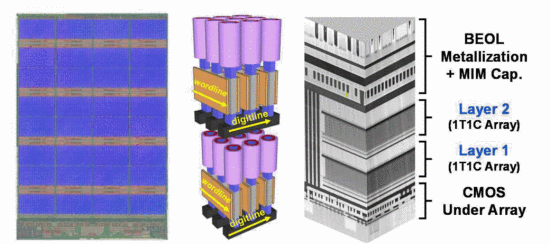

一款 32GB 双层三维堆叠非易失性铁电存储器,具备近 DRAM 性能

课题组侧重点与优势

参考文献

1.S. Mueller et al., “Ferroelectric Hafnia: A New Age for FRAM has Started,” 2024 22nd Non-Volatile Memory Technology Symposium (NVMTS), Busan, Korea, Republic of, 2024, pp. 1-6, doi: 10.1109/IEEECONF63530.2024.10830895. keywords: {Low voltage;Nonvolatile memory;Ferroelectric films;Electronics industry;Capacitors;Random access memory;Production;Lead zirconate titanate;FRAM;DRAM;stacked FRAM;${HfO}_{2}$;hafnia;embedded memory;standalone memory;coercive voltage},